Solved: easy to swap pin at ddr3 memory side? – message boards

@jschmitz,

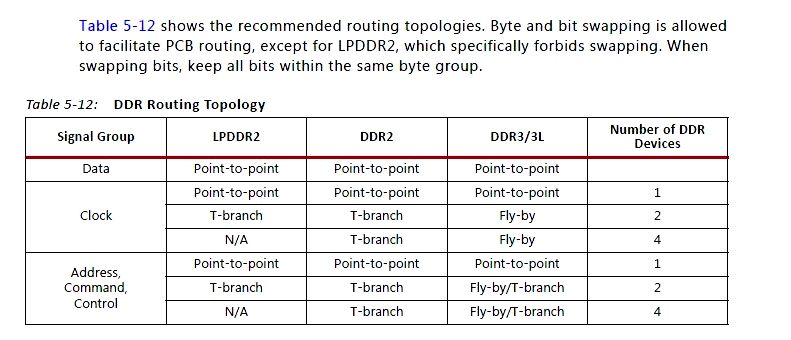

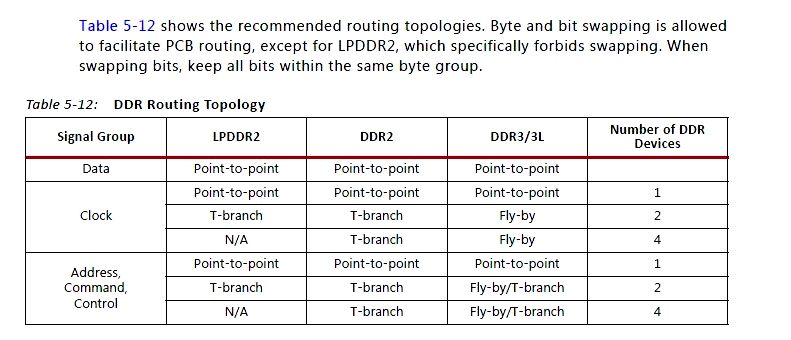

Controllers using more than just one component as well as some with simply one (Virtex-6 for MIG, for instance), is going to do write leveling. The active return DQ (“prime DQ”) for that write leveling could be whether single bit or even the entire byte lane. It can be the memory vendor. When the entire byte lane is active, then there’s no swap issue. But if perhaps one bit can be used, you’d have to be careful about swapping it.

NOTE: this publish concerns only DDR3 designs.

Executive Summary:

- The issue described in jschmitz’ publish is proof of a non-compliant memory controller design.

- A JEDEC-compliant DDR3 memory controller doesn’t have such bit-swap sensitivity with write leveling, or with every other transaction or function.

- Xilinx Virtex-6, Spartan-6, and Gen-7 memory controller IPs don’t have the issue explained jspaldings.

Lengthy technical explanation of DDR3 design and Jedec standard as it requires this:

- The JEDEC DDR3 standard doesn’t specify which DQ (inside a byte lane) will be the ‘prime DQ’. By requiring all non-prime DQs to become ‘0’, the JEDEC standard ensures recognition from the ‘prime DQ’ through the controller.

- DRAM device manufacturers aren’t obligated to determine or conserve a consistent and constant ‘prime DQ’ bit selection, in order to match Micron’s current design selection.

- DIMM/SO-DIMM manufacturers are permitted to (and can) swap DQ signals within byte lanes, rendering DRAM manufacturer’s prime DQ identification moot. A whole lot worse, two-rank modules might have united nations-matched DQ swapping for each one of the two ranks. [note: from JEDEC 21C — DQ-to-I/O wiring is proven as suggested but might be altered.]

- To be able to maintain compatibility with assorted DRAMs and modules, memory controllers are obligated to identify any DQ bit which can be ‘prime’.

This really is rather an essential issue.

The purpose of a business standard (JEDEC JESD79-3E, for instance) would be to allow and be sure industry compatibility. The JEDEC DDR3 standards (devices, modules) don’t specify a ‘prime DQ’. JEDEC views a specs from the ‘prime DQ’ unnecessary for industry compatibility.

Incidentally, there are several memory controllers (Freescale 8536 one thinks of) that do not ‘do the best thing’ regarding this very point. For example, this type of disadvantage is recognized as an ‘erratum’, as opposed to a ‘feature’, by Freescale (erratum, page 24).

@jschmitz,

Controllers using more than just one component as well as some with simply one (Virtex-6 for MIG, for instance), is going to do write leveling. The active return DQ (“prime DQ”) for that write leveling could be whether single bit or even the entire byte lane. It can be the memory vendor. When the entire byte lane is active, then there’s no swap issue. But if perhaps one bit can be used, you’d have to be careful about swapping it.

NOTE: this publish concerns only DDR3 designs.

Executive Summary:

- The issue described in jschmitz’ publish is proof of a non-compliant memory controller design.

- A JEDEC-compliant DDR3 memory controller doesn’t have such bit-swap sensitivity with write leveling, or with every other transaction or function.

- Xilinx Virtex-6, Spartan-6, and Gen-7 memory controller IPs don’t have the issue explained jspaldings.

Lengthy technical explanation of DDR3 design and Jedec standard as it requires this:

- The JEDEC DDR3 standard doesn’t specify which DQ (inside a byte lane) will be the ‘prime DQ’. By requiring all non-prime DQs to become ‘0’, the JEDEC standard ensures recognition from the ‘prime DQ’ through the controller.

- DRAM device manufacturers aren’t obligated to determine or conserve a consistent and constant ‘prime DQ’ bit selection, in order to match Micron’s current design selection.

- DIMM/SO-DIMM manufacturers are permitted to (and can) swap DQ signals within byte lanes, rendering DRAM manufacturer’s prime DQ identification moot. A whole lot worse, two-rank modules might have united nations-matched DQ swapping for each one of the two ranks. [note: from JEDEC 21C — DQ-to-I/O wiring is proven as suggested but might be altered.]

- To be able to maintain compatibility with assorted DRAMs and modules, memory controllers are obligated to identify any DQ bit which can be ‘prime’.

This really is rather an essential issue.

The purpose of a business standard (JEDEC JESD79-3E, for instance) would be to allow and be sure industry compatibility. The JEDEC DDR3 standards (devices, modules) don’t specify a ‘prime DQ’. JEDEC views a specs from the ‘prime DQ’ unnecessary for industry compatibility.

Incidentally, there are several memory controllers (Freescale 8536 one thinks of) that do not ‘do the best thing’ regarding this very point. For example, this type of disadvantage is recognized as an ‘erratum’, as opposed to a ‘feature’, by Freescale (erratum, page 24).

When we have your attention, can you occur to know which of the present Xilinx [soft mixed hard] memory controllers support either write leveling or read leveling for DDR3 ?

Thanks kindly,

— Bob Elkind

Resourse: https://forums.xilinx.com/t5/Memory-Interfaces-and-NoC/possible-to-swap-pin-at-DDR3-memory-side/td-p/